| www.tmatlantic.com

Test & Soldering Equipment On-line Store |

|

D.E.V.I.C.E. (Wiki)Calculators Services |

|||||

Filter by first letter

|

Logic state synchronization

The trigger is made in case all the signals being passed to the logic inputs of the logical function chosen cause the change of this function state for “true” or “false” when the clock input state is changed or stable (level timing). For oscilloscope logical synchronization there can be two ordinary scope input channels used as well as the external synchronization channel additionally. Such three-channel design allows, besides usual logical functions "AND", "OR", "Exclusive OR", setting such a rarely implemented function like majoritar: function result is considered true when the state at least on two input channels is "True".

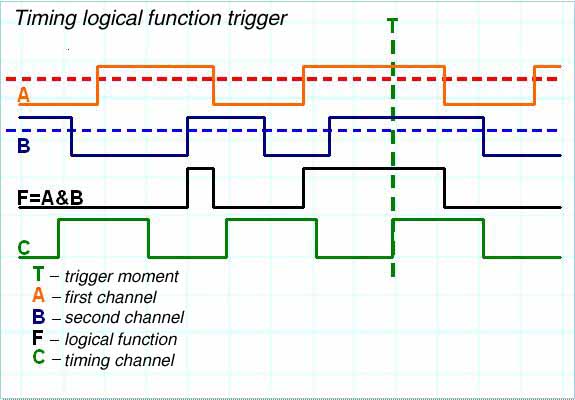

Pic.1. Algorithm of logic state synchronization. The picture below shows synchronization according to "AND" scheme of two input channels.

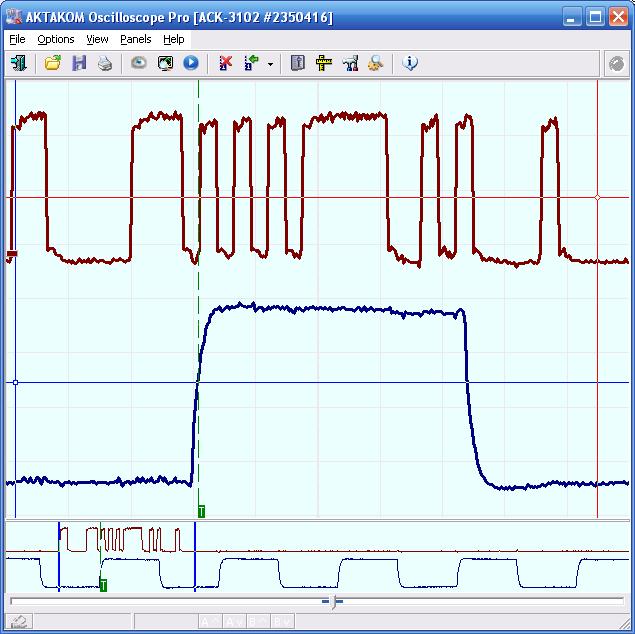

Pic. 2. The example of synchronization according to "AND" scheme of two ACK-3102 1T input channels. "A-B sweep" - a powerful tool for complex systems debugging developers since it allows analyzing and selecting almost any element of long consecutive digital codes blocks. A user can use combined triggering modes of A-B type. It’s possible to create a consistent combined event out of two different triggering events and to start making the sweep triggering when the second event is achieved. Therefore first of all it’s necessary to set up the conditions needed for A event which will start the sequence and afterwards - for B event which will be the final synchronization signal. Additionally it’s possible to specify the horizontal delay that should elapse between the events or the number of B events which should happen before sweep triggering.

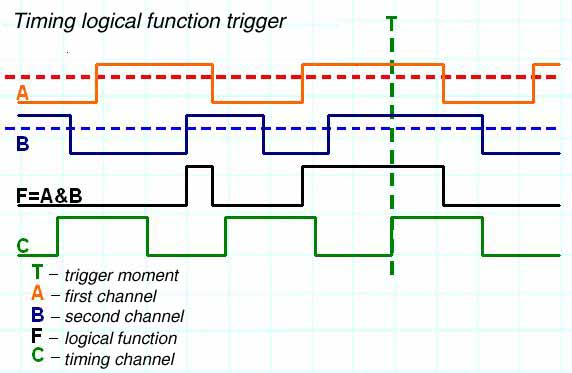

Pic. 3. Algorithm of timing logical function triggering. The following picture shows the third pulse triggering on 2 channel after the edge detection on 1 channel and a delay of 10 ms.

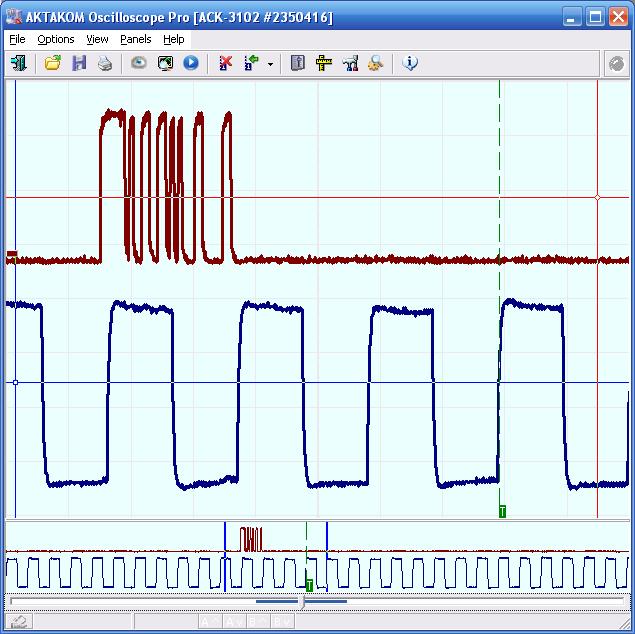

Pic. 4. Example of the third pulse synchronization triggering on 2 channel after the edge detection on 1 channel and a delay of 10 ms. |

Measurement History Events

Units Converter

|

|

Site mapPrivacy policyTerms of Use & Store PoliciesHow to BuyShippingPayment |